# Feldman Engineering

# 2.5D? 3D? What?

Overview of 3D Integrated Circuit Packaging and Test Challenges

Ira Feldman November 11, 2010

#### Outline

- Why 2.5D & 3D ICs?

- Building stacks

- TSV Processes

- ▶ 2.5D & 3D stacks

- Process & Test Flows

- Wafer Probe Solutions

- Key Organizations & Activities

- Future?

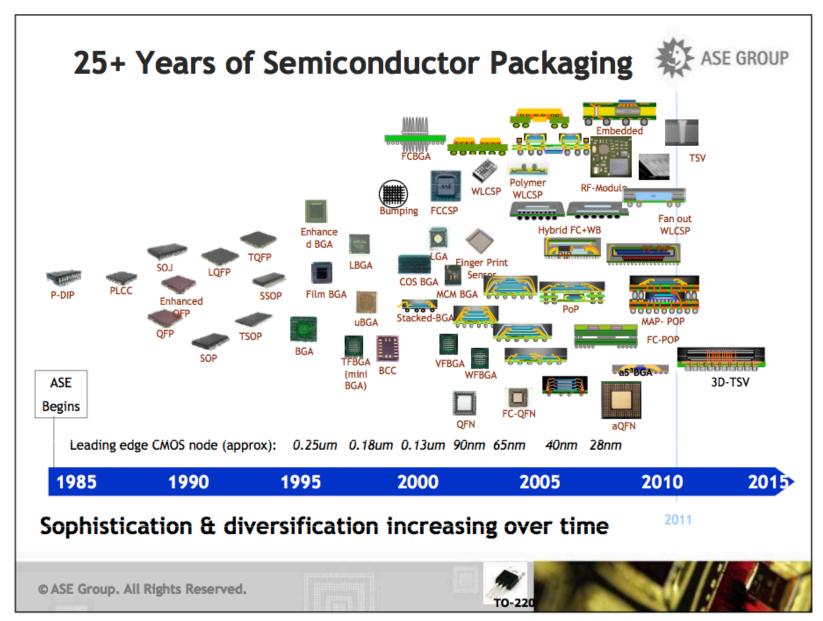

# Package Proliferation

"Backend to the Front Line" William Chen, ASE Group, SWTW 2011

#### Outline

- Why 2.5D & 3D ICs?

- Building stacks

- TSV Processes

- 2.5D & 3D stacks

- Process & Test Flows

- Wafer Probe Solutions

- Key Organizations & Activities

- Future?

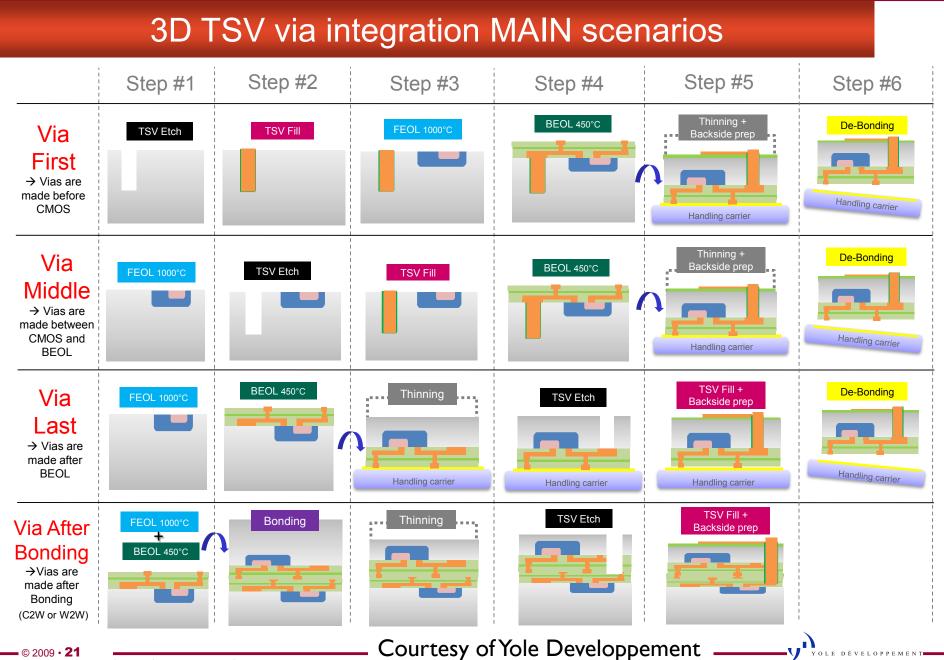

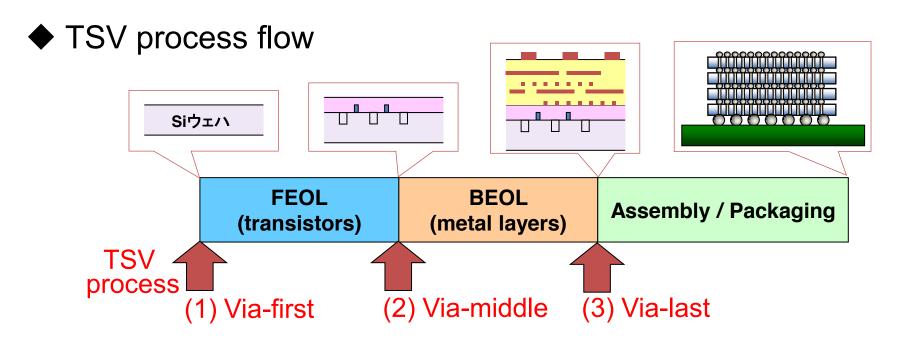

### **TSV Processing**

# 3D integration process options using TSV

◆ TSV interconnect methods

|      | (1) C2C: chip-to-chip  | (2) C2W: chip-to-wafer | (3) W2W: wafer-to-wafer |

|------|------------------------|------------------------|-------------------------|

| Pros | Flexible<br>Use of KGD | Flexible<br>Use of KGD | High throughput         |

| Cons | Handling, Bonding      | Handling, Bonding      | Same chip size, Yield   |

KGD: known good die

#### 1. Introduction to TSV-Based 2.5D- and 3D-SICs

### **Die Stacking**

#### **Endless Stacking Opportunities**

"Whatever your children can make using Lego bricks"

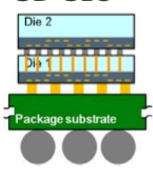

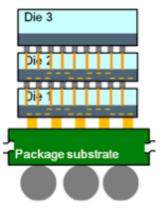

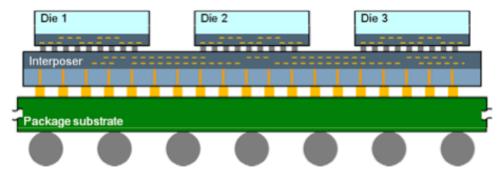

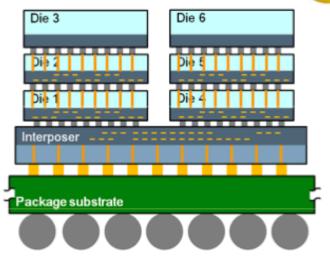

3D-SIC

2½D-SIC

"Wafer Probing on Fine-Pitch Micro-Bumps for 2.5D- and 3D-SICs", Erik Jan Marinissen (IMEC), Peter Hanaway (Cascade Microtech), et. al.

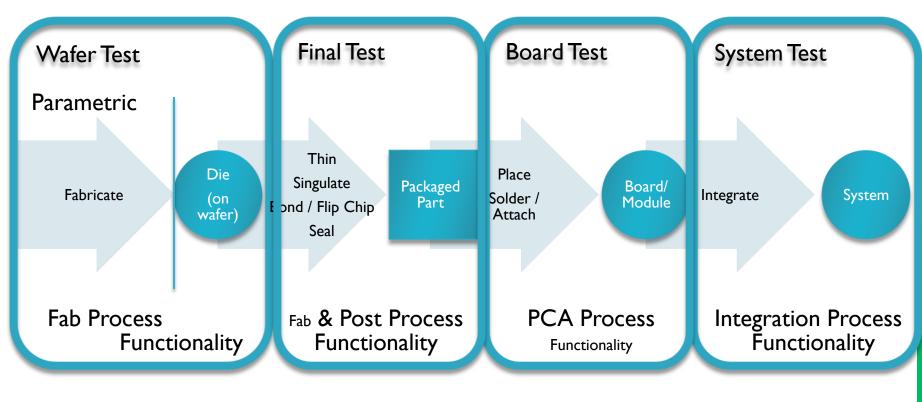

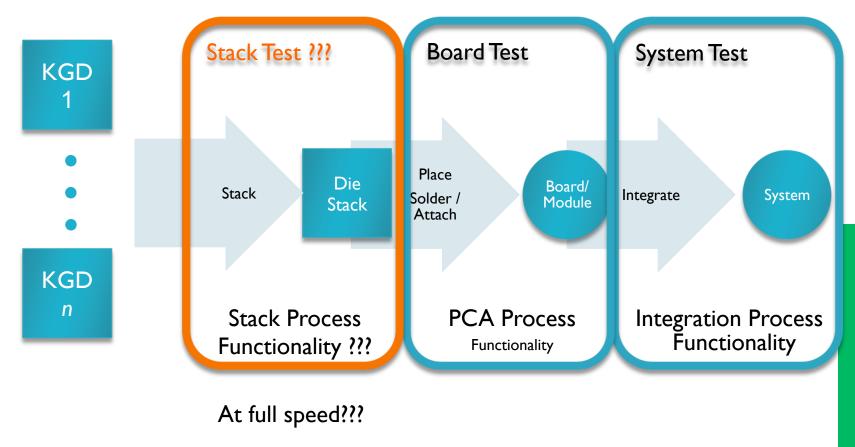

# Process Flow & Test Coverage

# **TODAY**

Partial to full speed

At full speed

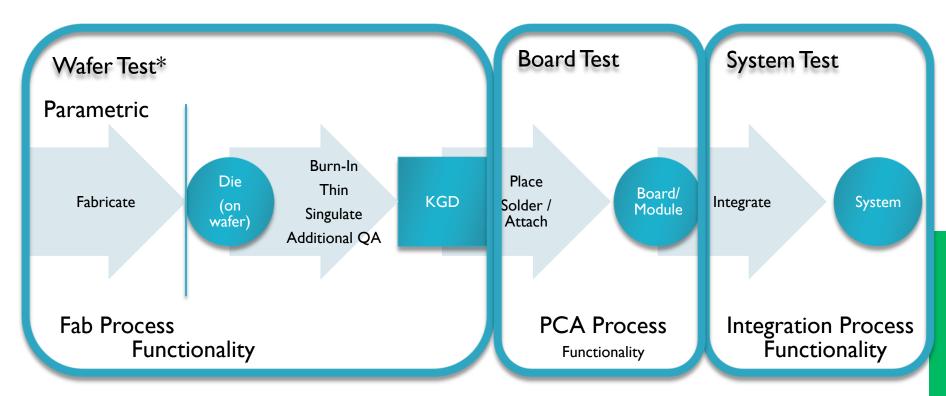

# Known Good Die - Flow & Test Coverage

### **TODAY**

At full speed

<sup>\*</sup> Predominant path to KGD is via wafer based testing. There are some solutions for die based socket testing such as Aehr Test's DiePak.

# Stacked Die – KGD (singulated)

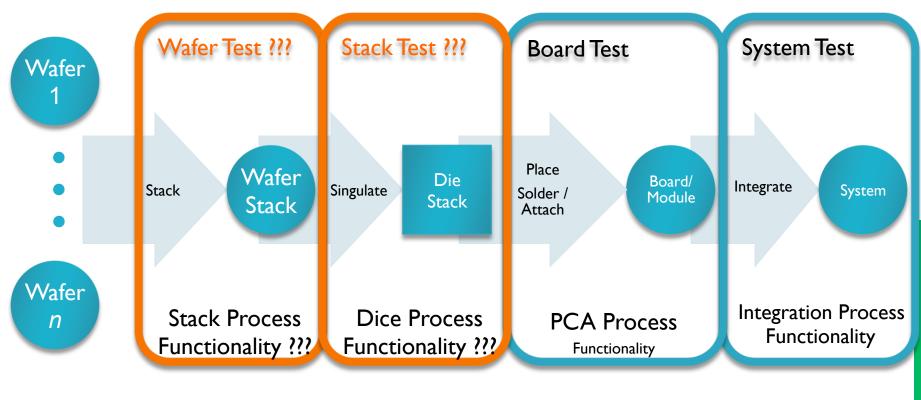

# Stacked Die – NKBD (wafers)

Wafers or reconstituted wafers of Not Known Bad Die:

- Thinned

- Partial to full speed tested

At full speed??? At full speed???

# Stacked Die – Sub Stacks (wafers)

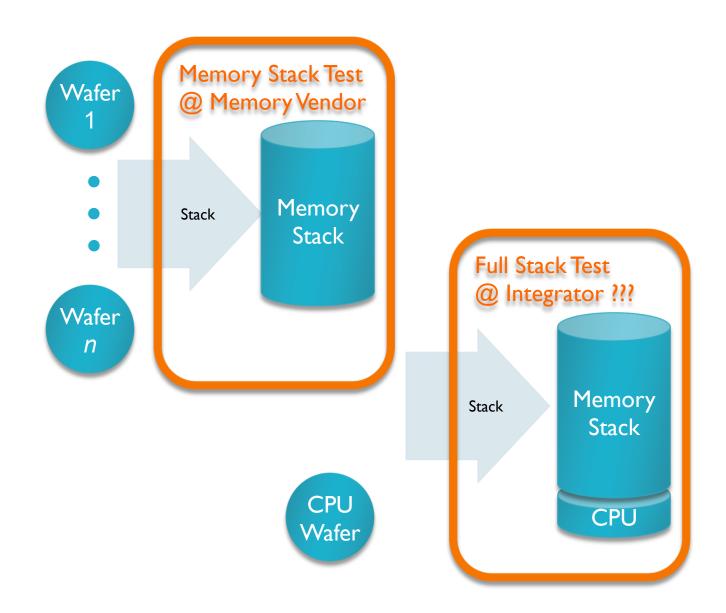

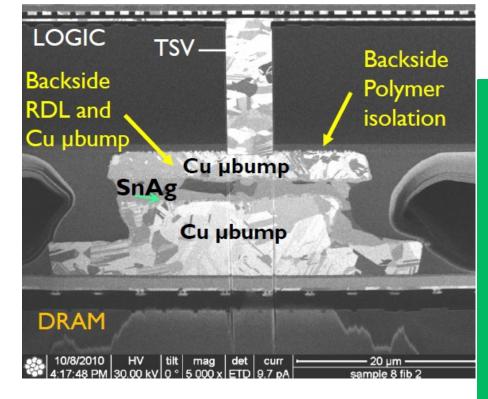

#### Reference Product / Structure / Flow

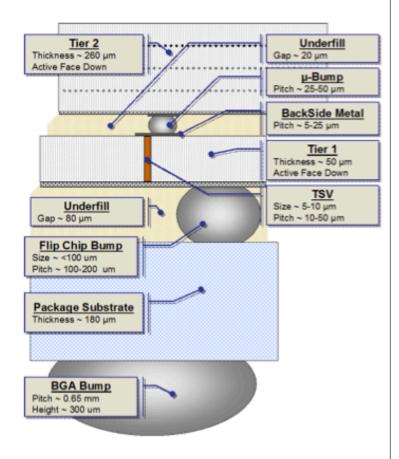

Reference product: Mobile wide I/O DRAM on logic ≤ 1.0mm Kings Kupis - SIPECON Tawan 2010 - Tapes Tawan Reference flow candidate Tier 2 to Tier 1 Molding, etc. Tier 1 die attach

#### Reference structure

"3D TSV Program Overview – Presented to GSA Oct 20, 2011" Sitaram Arkalgud, SEMATECH

20

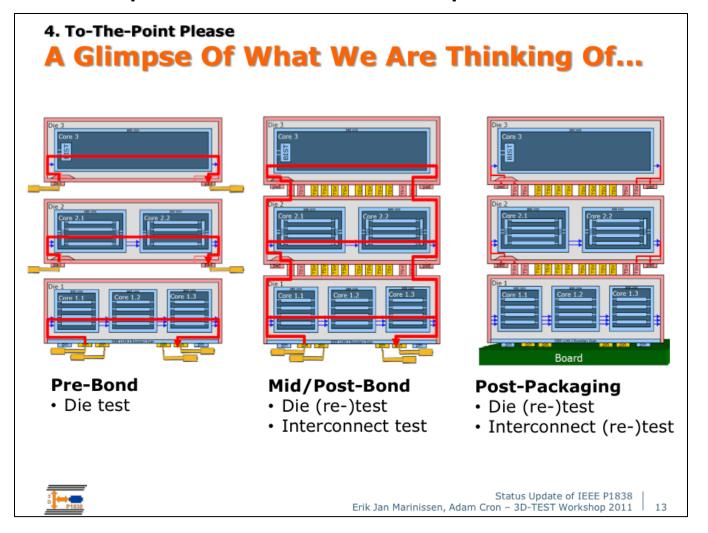

# Scan Testing

- Provide access and control to cores at all test steps

- If proper infrastructure (P1838) & connectivity is present

- Does not replace full access to all "pads" for KGD.

#### Outline

- Why 2.5D & 3D ICs?

- Building stacks

- TSV Processes

- 2.5D & 3D stacks

- Process & Test Flows

- Wafer Probe Solutions

- Key Organizations & Activities

- Future?

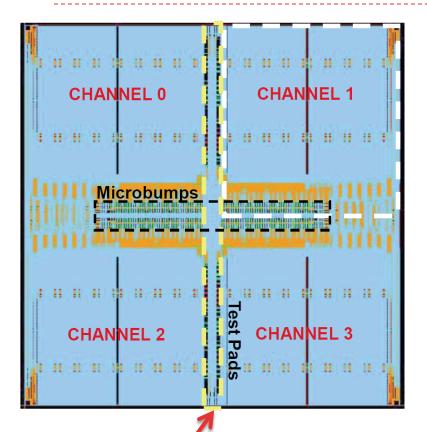

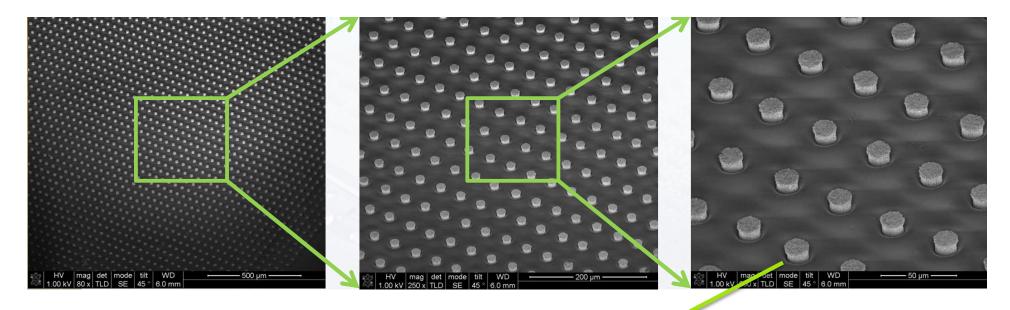

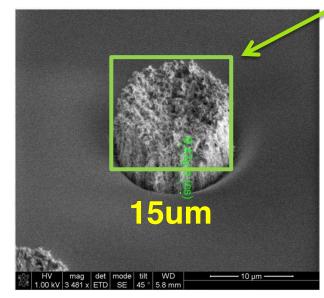

# Mobile DRAM predecessor to Wide I/O

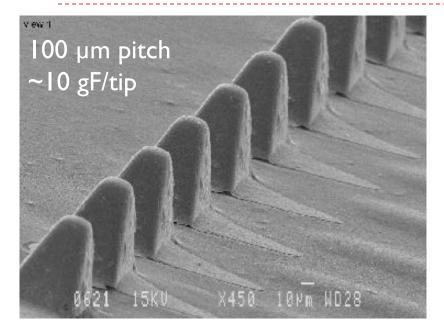

Al pads (muxed) to test with existing probe technology > 1000 micro-bumps 50 µm pitch array

"A I.2V I2.8GB/s 2Gb Mobile Wide-I/O DRAM with 4×I28 I/Os Using TSV-Based Stacking" Jung-Sik Kim, et.al., Samsung Electronics, ISSCC 2011

# Silicon Valley Test Workshop 2011

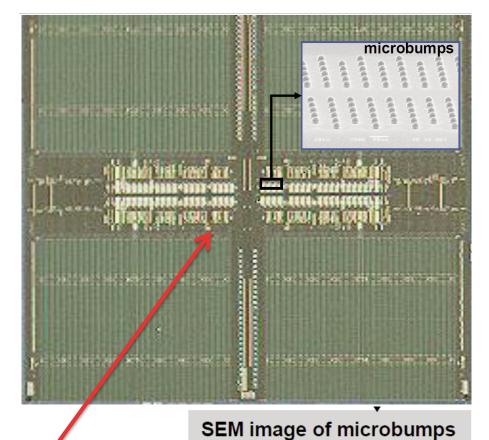

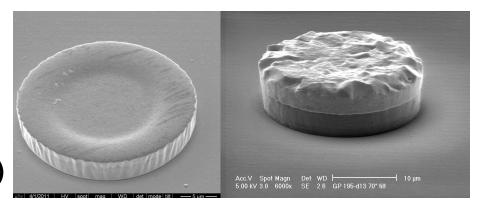

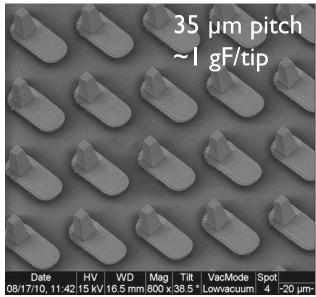

# Electroplated Micro-Bump Bonding

Cylindrical bumps

Side I: Cu (5 µm)

Side2: CuSn (5  $\mu$ m + 3.5  $\mu$ m)

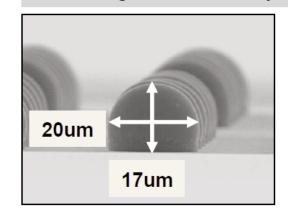

• Size (today)

Diameter: 25 µm

Pitch : 40 μm

Scaling down...

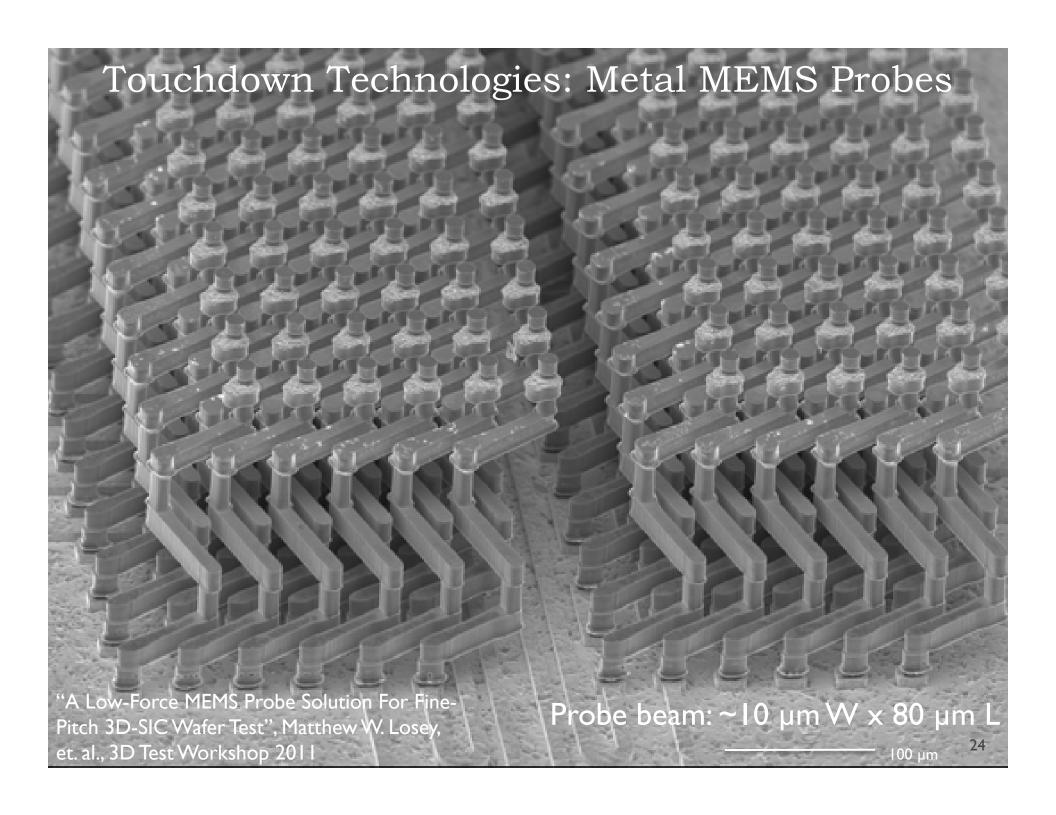

#### FormFactor: NanoPierce Contact

Metal "NanoFiber" contact element

# Silicon Valley Test Workshop 2011

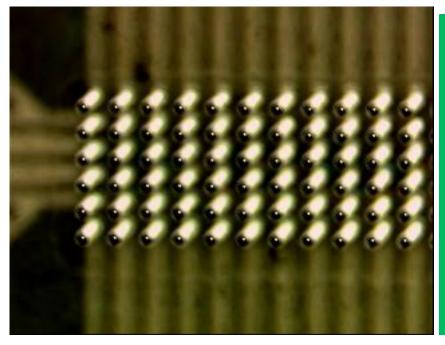

#### Cascade Microtech: Lithographically Printed

Scale by K XYZ/K

Force/K<sup>2</sup>

Fully-routed 6 x 50 array at 40 x 50  $\mu$ m pitch New space transformer technology

"Probing Strategies for Through-Silicon Stacking", Eric Strid, et. al, 3D Test Workshop 2011

#### Outline

- Why 2.5D & 3D ICs?

- Building stacks

- TSV Processes

- 2.5D & 3D stacks

- Process & Test Flows

- Wafer Probe Solutions

- Key Organizations & Activities

- Future?

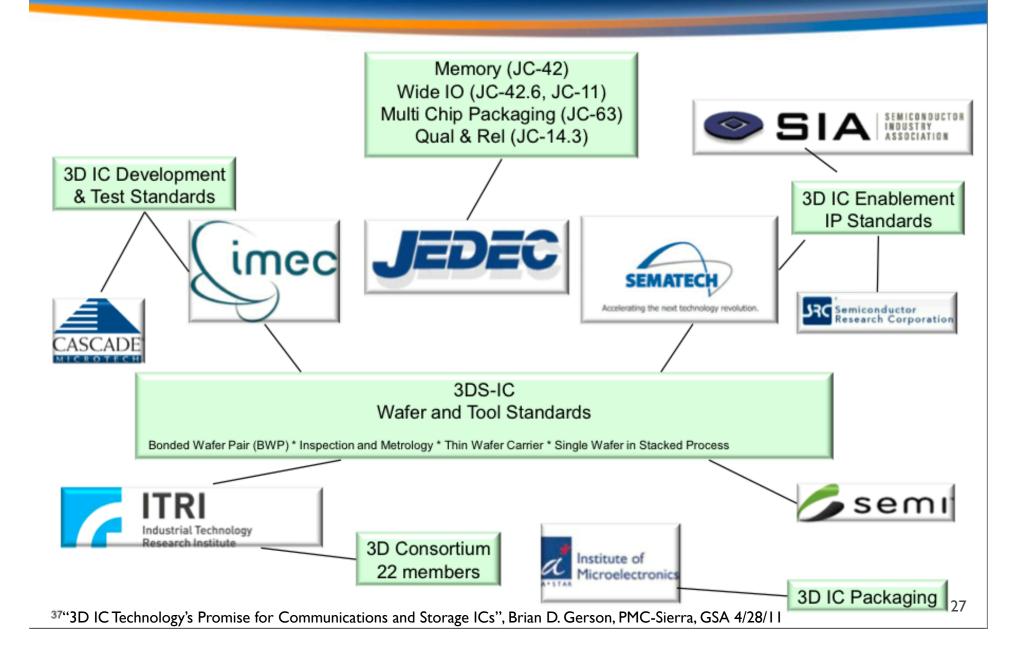

# **Developing Eco-system Standards and Clusters**

# Organizations & Programs

- ► IEEE P1838 Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits <a href="mailto:standards.ieee.org/develop/project/1838.html">standards.ieee.org/develop/project/1838.html</a>

- Semi wiki.sematech.org/3D-Standards

- ▶ Sematech 3D Program <u>www.sematech.org/research/3D</u>

- Unit Process, Module Development, Enablement Center

- Global Semiconductor Alliance 3D-IC Working Group www.gsaglobal.org/3dic

- JEDEC Wide I/O <u>www.jedec.org</u>

- ▶ IMEC <u>www2.imec.be</u>

- Industrial Technology Research Institute (ITRI) <a href="https://www.itri.org.tw">www.itri.org.tw</a>

- ▶ A\*Star Institute of Microelectronics <u>www.ime.a-star.edu.sg</u>

#### Recent Conferences

- SA Memory Conference (Mar 'II) www.gsaglobal.org/events/2011/0331/program.aspx

- IEEE Semiconductor Wafer Test Workshop (June '11 & '12) www.swtest.org

- ATE Vision 2020 (w/Semicon West Jul '11) www.atevision.com

- Semicon Taiwan SiP Global Summit 2011 (Sep '11)

- ▶ 3D IC Test Forum <a href="mailto:semicontaiwan.org/en/node/1566">semicontaiwan.org/en/node/1566</a>

- ▶ 3D IC Technology Forum <u>semicontaiwan.org/en/node/1571</u>

- IEEE International Workshop on Testing Three-Dimensional Stacked Integrated Circuits (w/ITC – Sep 'II / Nov 'I2) 3dtest.tttc-events.org

- ▶ MEPTEC 2.5D, 3D and Beyond Bringing 3D Integration to the Packaging Mainstream (Nov 9, 11) <a href="https://www.meptec.org">www.meptec.org</a>

- MEPTEC-Semi KGD in an Era of Multi-Die Packaging and 3D Integration (Nov 10, 11) <a href="https://www.meptec.org">www.meptec.org</a>

#### Outline

- Why 2.5D & 3D ICs?

- Building stacks

- ▶ TSV Processes

- ▶ 2.5D & 3D stacks

- Process & Test Flows

- Wafer Probe Solutions

- Key Organizations & Activities

- Future?

#### TBD - To Be Determined

- Yield

- Preferred Via Process

- Singulate dies before or after stacking

- Wafer probe and handling of die stacks on wafer or singulated stacks

- Business models who is responsible for what

#### **Future**

- Hard work getting it to work!

- Increased test complexity earlier in process

- Shrinks especially microbumps and pitch

#### Thank You!

Ira Feldman ira@feldmanengineering.com

Visit my blog www.hightechbizdev.com for additional resources.

#### Other References & Resources

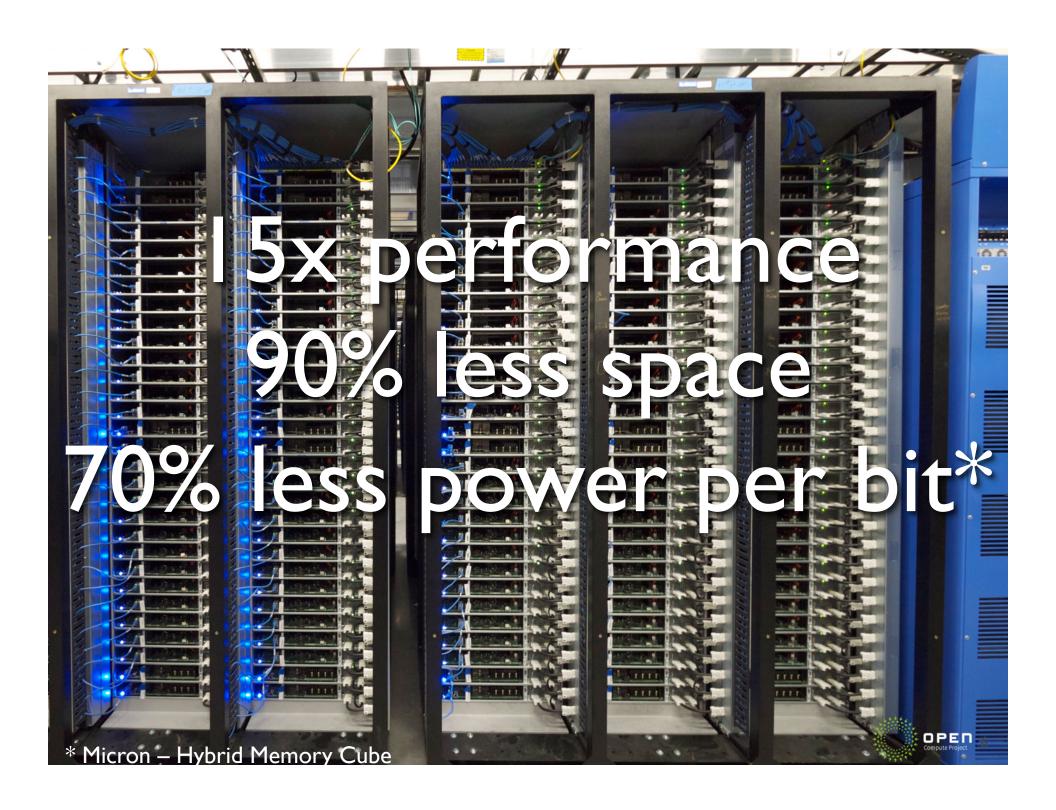

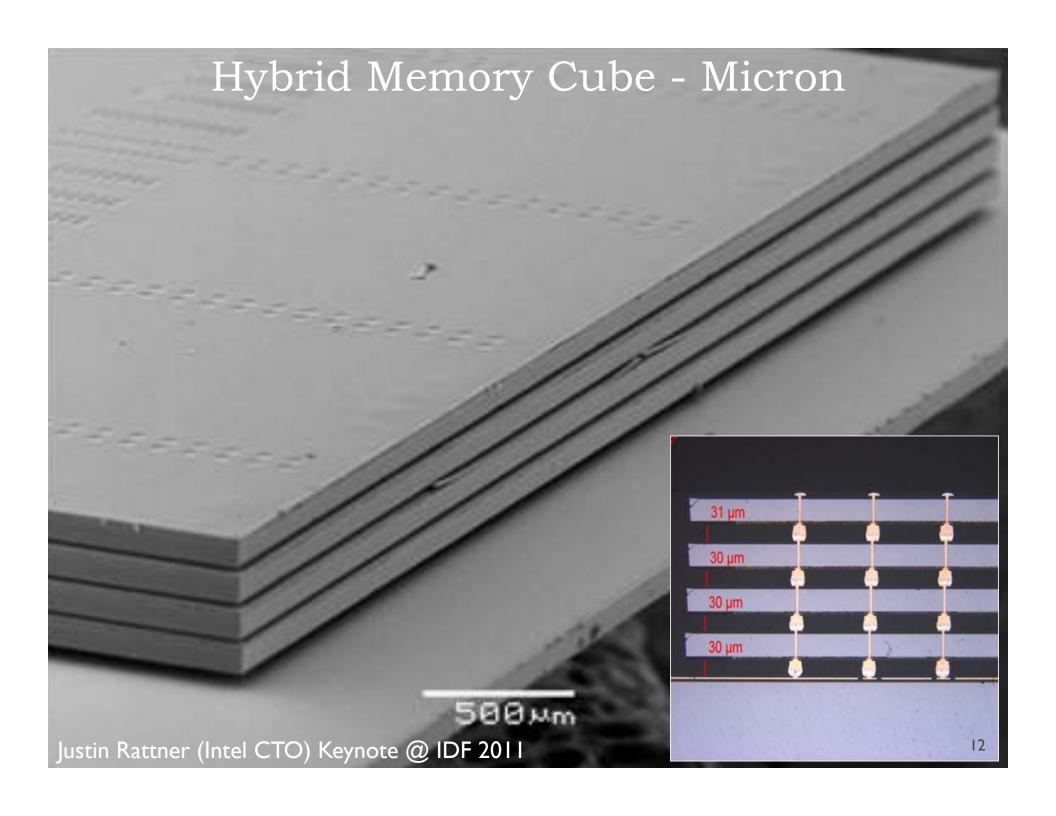

- Hybrid Memory Cube Consortium www.hybridmemorycube.org

- ▶ 3D-IC Alliance <u>www.3d-ic.org</u> (event & blogs/paper listing)

- Discussion groups / 3D news:

- www.3dincites.com

- www.3d-ics.com

- ▶ 3D-IC group on <u>www.linkedin.com</u>